Half_adder f(input1,input2,answer,carry) įull_adder f(input1,input2,carry,answer,carry) Įndgenerate endmodule // : FPGA projects, Verilog projects, VHDL projects // Verilog project: Verilog code for N-bit Adder // Verilog code for half adder module half_adder(x,y,s,c) Įndmodule // half adder // fpga4student. The examples include a Gray-to-binary code converter, a BCD-to-decimal decoder, a modulo-10 counter, an adder-subtractor, an adder and high-speed shifter.

Use full adder step-by-step for bit pairs, so when finish last step, we have final result.ġ.// : FPGA projects, Verilog projects, VHDL projects // Verilog project: Verilog code for N-bit Adder // Top Level Verilog code for N-bit Adder using Structural Modeling module N_bit_adder(input1,input2,answer)

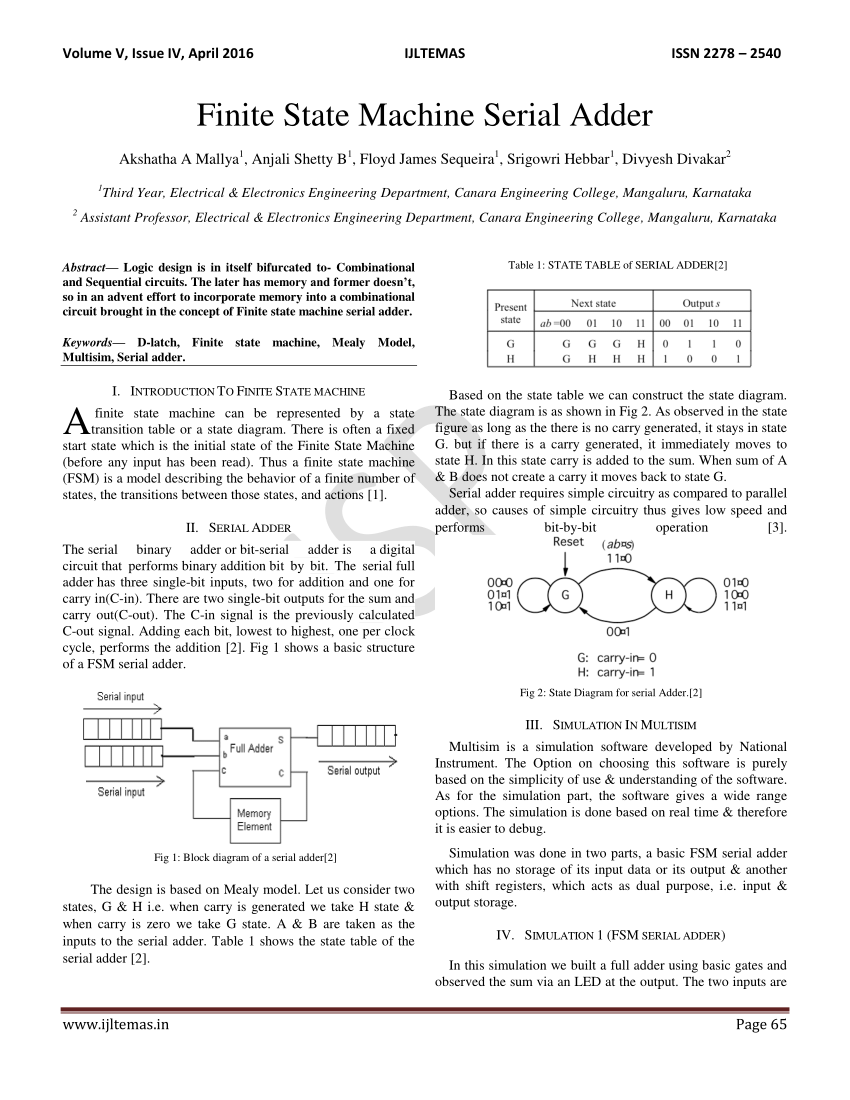

Always, first bit is 0, because of there isn’t any operation before first bit pair so there is no ‘carry in’ value.) Others: carryValuesFromFullAdders (5 bit) (With this, we store carry values and use this value next step. Yes, you read correctly 4bit subtractor using full adder by concept of Instantiation was explained in great detailfor more videos from scratch check this li. If we want to write an algorithm for these, how to do this? A subtractor is is addition with complement in a binary sysstem That is A and b are inputs: For A - B, first complement B to B. Module fadder (A, B, Cin, Sum, Cout) input A, B input Cin output Sum output Cout wire t1,t2,t3,t4 xor x1. Then I am using that to write code for 4 bit adder subtractor. At first I have written verilog code for 1 bit full adder. Step-3 : Verilog HDL code for Full Adder (Design Part). Continue on app Combinational Logic Circuits. The shift registers are loaded with parallel data when the circuit is reset. Verilog Code For Serial Adder Subtractor Overflow. Detailed description of Serial Adder, Serial Subtractor and Serial Adder-Subtractor. In serial adder three shift registers are used for the inputs A and B and the output sum. Always, the carry value is add to next step and the sum value is written to result. The Verilog code for the top-level module of this design is shown in Figure 3. Serial-Adder Serial Adder: Serial adder consists of the shift registers and the adder FSM.

You know how to do addition using step-by-step.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed